目次

- 1 はじめに

- 2 Questa Intel FPGA Edition のセットアップ

- 3 NativeLink で起動したシミュレータのコマンドライン操作

- 4 シミュレーション・ライブラリの生成

- 5 前提

- 6 ライブラリ生成

- 7 コンパイラが Quartus Prime であるか否かを判定する

- 8 プロジェクトを再生するための必要十分なファイル群

- 9 IP Catalog の ROM 等の IP で MIF ファイルを相対パス指定する

- 10 LPM_XYZ IP の RTL シミュレーションのバグ (Quartus Prime Lite 23.1std)

- 11 Platform Designer で作った子階層の型名を変更する

- 12 Platform Designer で階層構造を作る例

はじめに

時々必要になるが、その時には多分忘れているであろう知識を書き残しておく。

Questa Intel FPGA Edition のセットアップ

Quartus Prime のインストール時に同時にインストールできる(インストーラの画面でチェックを入れる)が、そのままでは使えない。下記のページにあるように、ライセンスの設定が必要。これは罠。

Questa* – Intel® FPGA Starter Edition ライセンスファイルの取得および設定方法

NativeLink で起動したシミュレータのコマンドライン操作

NativeLink 機能を使うと IP を含むプロジェクトが正しくシミュレーションできるよう、Quartus Prime がお膳立てしてシミュレータを起動してくれる。そこまではいい。

では、その後でテスト・ベンチを更新したり、新しく自作モジュールを追加したりした後に Quartus Prime に戻らずに(つまりシミュレータを再起動せずに)再コンパイルとシミュレーションの再実行を行うにはどうすればよいか?

Quartus Prime のプロジェクト > Settings > EDA Tool Settings > Simulation > Output directory で示された場所(起動したシミュレータのカレント・ディレクトリと一致する)にシミュレーション用の Tcl スクリプト・ファイルが生成される。スクリプト・ファイルの名前は [top entity name]_run_msim_rtl_systemverilog.do である。これをエディタで開くと何が行われているのか解る。冒頭はディレクトリの準備や IP のコンパイルであり、自作の RTL ファイルのコンパイル(vlog ...)がそれに続く。その後にシミュレーション実行(vsim ..., add wave *, run -all)がある。

もちろん、この do ファイルを Tcl コンソールから再実行してもよいが、一般にベンダ提供の IP のコンパイルには時間が掛かるので、自作 RTL ファイルのみを再度コンパイルしたいことが多い。その際は前記 do ファイルをヒントに、変更・追加した RTL ファイルのみをコンパイルするコマンドを Tcl コンソールに打ち込み、vsim ..., run -all を再実行すればよい。

シミュレーション・ライブラリの生成

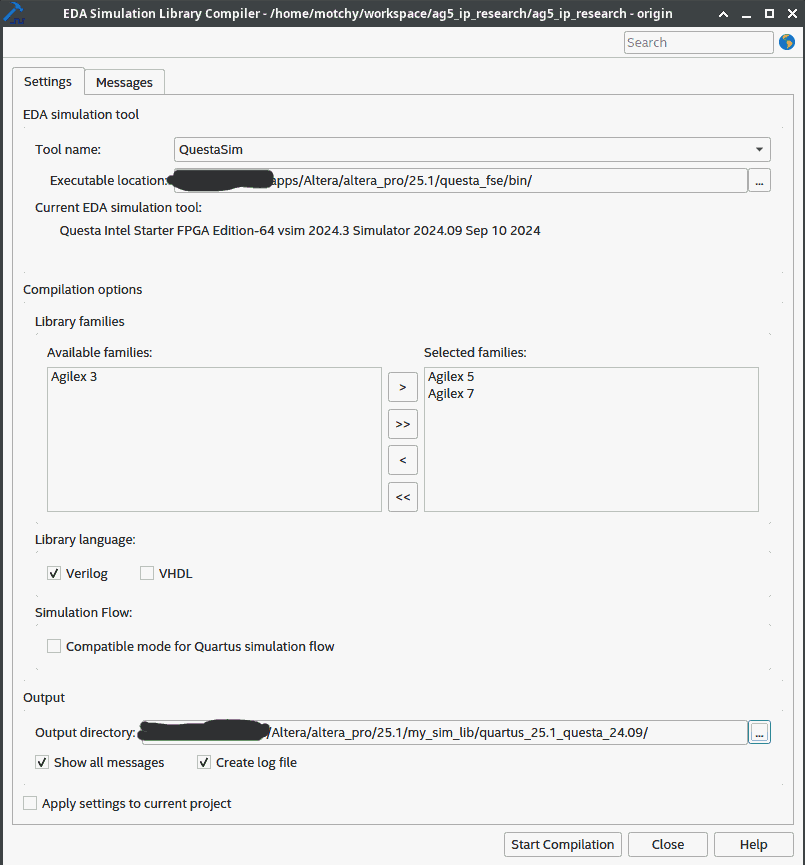

Quartus Prime とシミュレータのバージョンの 2 つの組に対して 1 セットのライブラリを生成する必要がある。ここでは Quartus Prime Pro と Questa Intel Starter FPGA Edition の組み合わせを前提とする。両者のバージョンは次の通り。

- Quartus Prime Pro 25.1

- Questa Intel Starter FPGA Edition-64 vsim 2024.3 Simulator 2024.09 Sep 10 2024

前提

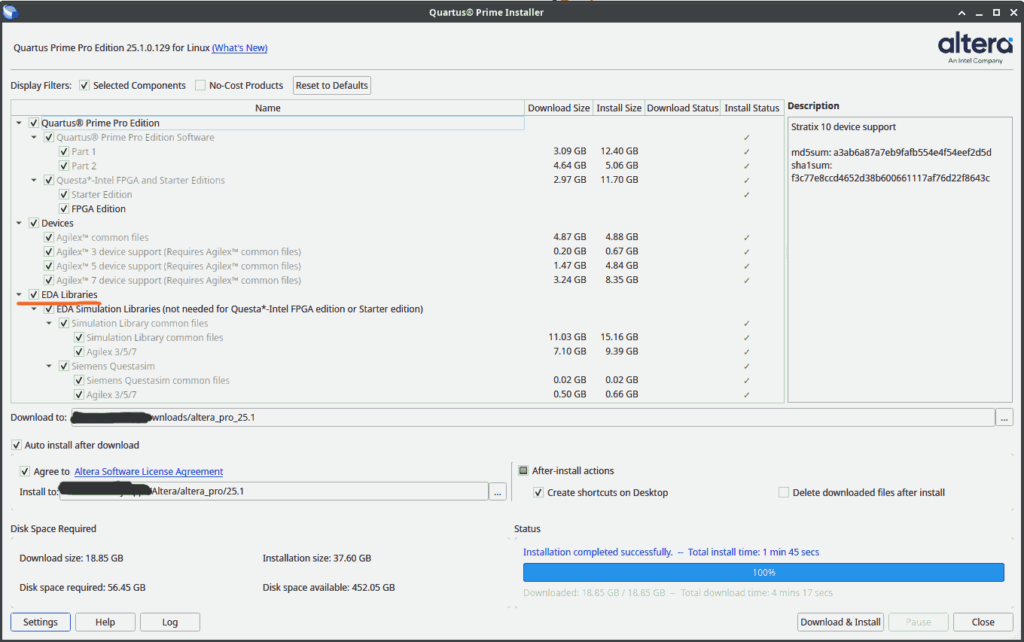

EDA Simulation libraries が必要である。 インストール済か否かは Quartus Prime Installer を使って確認できる。不足していればインストールする。

“not needed for Questa*-Intel FPGA Edition or Starter Edition” と書かれているが,これは間違いである。もしインストールされていなければ,<Quartus Home>/eda/sim_lib 下に altera_primitives.v, 220model.v 等が存在せず,ライブラリ生成に失敗する。

ライブラリ生成

Quartus Prime の メニューバー > Tools > Launch Simulation Library Compiler から EDA Simulation Library Compiler を起動する。設定内容は次の通り。

画面右下の Start Compilation ボタンを押すと生成が始まる。マシンの性能に依るが,所要時間は 20 分程。ライブラリのデータ・サイズは 3 GiB 程度である。

コンパイラが Quartus Prime であるか否かを判定する

下記の Web ページで紹介されているように、ALTERA_RESERVED_QIS が定義されているか否かで判る。

How to determine that synthesis is done in Quartus?

プロジェクトを再生するための必要十分なファイル群

Quartus Prime のプロジェクトを Git でバージョン管理する際に、どのファイルを管理対象とすれば(つまりそれ以外は消えてもいい)必要十分であるか知っておく必要がある。それは次のファイルである。

Quartus Prime Lite Edition / Pro Edition 共通

- プロジェクト情報ファイル:*.qpf, *.qsf

- 自分で作った HDL ファイル(*.sv 等)と制約ファイル (*.sdc)

- Platform Designer の情報ファイル:*.qsys

Quartus Prime Lite Edition 特有

IP 情報ファイル:*.qip, *.sip (前者が論理合成用、後者がシミュレーション用)qsys フォルダの中にもあったりする。

Quartus Prime Pro Edition 特有

IP 情報ファイル:*.ip これらは qsys フォルダの中にもあったりする。

アーカイブ機能を使う方法

Quartus Prime にはプロジェクトをアーカイブして *.qar ファイルを作る機能がある。そのウィザードの ‘Advance’ オプションから ‘source control’ を選択して生成されるアーカイブの中身を Git で管理してもよいだろう(試したことはない)

IP Catalog の ROM 等の IP で MIF ファイルを相対パス指定する

下記の Web ページによると *.qpf を起点とする相対パス指定が可能。./ で始める。

LPM_XYZ IP の RTL シミュレーションのバグ (Quartus Prime Lite 23.1std)

ここでは LPM_DIVIDE を例に選んで述べる。少なくとも LPM_DIVIDE については、NativeLink を使う RTL シミュレーションにはバグがあり、IP の出力が Hi-Z のまま動かない。これを回避するには <Quartus Prime installation directory>/eda/sim_lib/220module.v に集められている module から対象のモジュール(今は lpm_divide)の部分をコピーして別名、例えば lpm_divide_sim.v として所望のディレクトリに保存し、(ウィザードで生成された IP ではなく)これを使うように自分の HDL コードを書き換える。モジュールはパラメータ化されているので、適切にパラメータを与える。

前記 220module.v の中身はあくまでシミュレーション・モデルと思われるので、配置配線に於いてはこちらではなくウィザードで生成された IP を使うべきだと考えられる。どちらを使うか、パラメータまたはマクロで切り替えられるようにしておくとよい。

Platform Designer で作った子階層の型名を変更する

検証環境:Quartus Prime Lite 23.1std

Platform Designer で ‘Add a new subsystem to the current system’ すると子階層が作られる。その際に「インスタンス名」はウィザードで指定できるが、「型名」は常に ‘subsystemA’ となる。これを変えるには次の手順が有効である。

- 一旦プロジェクトを閉じて VS Code 等でプロジェクトのフォルダをワークスペースとして開き、配下のファイル群中の ‘subsystemA’ を全て所望の型名に書き換える。

- subsystemA を名前に含むフォルダとファイルの名前の subsystemA の部分を所望の型名に書き換える。

Platform Designer で階層構造を作る例

Platform Designer で階層構造 (sub-system) を作り、かつ sub-system の配下の複数の Avalon-MM Agent の agent インタフェースを仲介機構

(Avalon-MM Pipeline Bridge) で⼀つの agent インタフェースにまとめて上位の階層に⾒せる具体例。